4月19日,这一天上海的早晨阳光空气都很好。一早我们顺着沙丁鱼二号罐头被运往了集中站——张江高科。走了五分钟的路程到达了DVCon的大会举办酒店,博雅酒店。这个酒店的地理位置很好,南侧禁邻着中兴办公大楼,北侧便是IC从业者的吃喝交谈的平常去处,创奇商业广场。去之前还在考虑,作为DVCon的第一届大会,会有多少从业者参加,然而在步入会场的一刹那,这一点点疑虑便被打消了。DVCon在美国举办了已经超过30个年头,在欧洲的慕尼黑和印度的班加罗尔也已经举办得成熟了,而中国作为强劲的IC新大陆也日益收到了全世界的关注,DVCon和Accellera及时地举办了第一届中国区的设计验证会议很能说明这一点。

在大会主席刘红亮的致辞中,我们得知了这次大会的背后是众多的行业精英促成了这一届的举办,与会的两百多位听众也来自于不同的公司,不单单是上海张江,而且也包括路桑在内的全国各地的工程师。在会议的keynote环节中,Mentor Graphics公司(A Siemens Business)主席和CEO Wally Rhines博士对目前的设计验证领域中存在的挑战做了一个系统层面的分析。

从中我们可以感受到的是,除了芯片面积的增加、单位晶体管的密度增加和晶体管单个价格的下降以外,带来的更多的是成倍的验证复杂度提高。面对验证的复杂形势,我们不单单需要的是功能验证,还需要考虑时钟域、复位域和电源域的验证、能耗(low power)域与性能域(performance)的评估、安全域和软硬件协同开发等方面。包括传统的逻辑仿真领域在内,目前还有的形式验证、虚拟建模、FPGA原型验证和emulation技术都有各自的市场,而且这些市场在很大的层面上是相互交叠,伴随着芯片面积的增大,这些技术在一个项目上会被同时使用,服务于不同的验证要求。

这么多繁复的EDA工具和技术的涌现和升级,都从侧面反映了验证领域和验证工程师们的项目生活,那就是不断地学习和实践。比起老牌的欧美市场,我们国内的公司在从旧的技术跳转到新的技术上面,包袱小步子大,这一点无论是从分享到的行业数据还是从我们这两年的面试情况都可以匹配到。然而新鲜的技术、强劲的工具马达也可能使得国内的中小公司在面对着EDA公司给出的解决方式时,会有疑惑的地方。这些疑惑在于如何组合不同公司之间的工具,使得它们最终可以最优地服务于一个目的。不同公司之间的工具在上面提到的各个验证领域层面,都有自己的“锚点”来企图占领该细分领域的份额,而实际上同一家公司的产品是能更好地完成一个验证周期的工具闭环链。这一消息对于新成立的公司可能是喜忧参半,好的方面是就像进了“小米之家”买买买就是了,担忧的一点是一旦没有了更充分的选择权恐怕没有更多的空间去尝试新的工具和方法。

令我们能减少一点担忧的是,这次大会参展的EDA工具商还是有着三个大玩家和其它的小玩家,尽管过去的一年半导体行业不断上演着收购和并购的故事,EDA工具领域里仍然有着活力澎湃的小玩家来推出它们的方法,这也反映出了验证市场还有足够的空间来buy in它们的idea,这是个有趣的现象,至少看得出验证领域也能有新的点子可以通过升级生产工具来提供效率,尽管没有足够的可用来提交专利的空间,也丝毫不影响验证技术的重要性。在大会中,我们也听到了DVCon的代表在谈到Accellera积极促进各项IEEE标准事务的进展,这其中就包括了最近几年内标准下载量最多的SystemVerilog,还有即将成为标准被UVM-1.2。

路桑在这次大会中,继续感受到了EDA的三个大玩家的合作和竞争关系。正是这种市场关系为我们验证技术的提高带来了十足的动力,竞争的关系可以看到三家公司都在会场亮出了它们各自的emulation“大杀器”,这一利器在经过了20多年的沉寂之后重返江湖,在大陆市场也越来越受到青睐。路桑对这一技术的期待正如对之前formal工具的评价一样,它们都仍然需要经过工业市场的调校,例如formal工具的发展策略已经不简单局限于为property语言提供平台来进行功能分析,而且有更多实际的工业需求和反馈对formal技术提出了另一个方向的要求,那就是formal工具本身就应该自动生成一些断言或者更好地协助那些非专业property的验证人员来享受到所谓“just click button”的快感,如果将验证人员不能很好地写出合适的property这一问题解决,那么路桑有充分的理由看好formal验证的市场。

而对于emulation应用而言,最大的推广阻碍在于珍贵资源的准入门槛过高和资源本身的不合理利用。这一个个的利器emulator,块头大速度快,且便于调试,对于吭哧吭哧在simulator上面喘气的动不动就上亿门的芯片无疑是一个更大的阳光浴场。然而令各个公司都要三思的还是这些大家伙的可观售价。一个福音是,目前EDA大佬们也在想着法子推广这一新的技术,不久的将来,通过将simulator和emulator(还有FPGA)的编译、仿真平台也趋于统一化,那么至于后台在用哪一种技术运行不再是验证工程师们需要关心的问题。也正因为这一个大的趋势,EDA公司们不单需要对现有simulator提供云端的服务,也更紧要的是为emulation提供云端的服务,通过合理利用资源池可降低小公司享受到这一黑科技的门票钱。

EDA公司们也都是互相盯着彼此的动作,他们不但有着竞争的关系,最近的十年也开始懂得了合作,朝着标准化的方向共同努力,而不再是各自为阵,打着三分田的算盘。如果追溯一下十年前的验证方法学,那个时候SV语言还没有一统江湖,老的HDL语言也还有验证的份额,至于e和Vera语言还都有着各自的客户,而在这些语言之上的方法学eRM/VMM/AVM还都各自繁荣,似乎有着战国诸侯的割据势力,而由此封闭起来的工具、语言和方法学支持可叫验证工程师和公司们格外被动,这带来的跨语言、跨平台的学习成本叫用户在尝试平台切换时都望而生畏。这种各自封闭的生态环境在SV和OVM、UVM的发展上面得到了改善。最后,一个阶段性的成果是,EDA公司们在互相的斡旋妥协下,选择了SV和UVM在2010年以后的市场统一。有了这个珍贵的共识,无论是EDA厂商还是IC公司,在逻辑验证领域上便有了更多的跨平台跨厂商的可能性。

这种在基础层面的统一,路桑认为对整个验证技术的发展是大有裨益的,而各个公司对于UVM和新标准的贡献,都将促成整个验证领域的不断推进。在这一背景下,我们很惊喜地看到,Accellera主导的PSS(Portable Stimulus Specification)标准已经在积极的推进。简单而言,发起PSS标准的初衷是由于目前还没有一个标准的方式在各个平台上面实现可以复用的激励形式,而该标准就是为了使得公司可以通过某种新的语言和形式来划定激励的形式,从而由该格式得出其它现有的激励形式,譬如C测试或者UVM测试代码。

关于PSS标准的设定和发展情况,路桑听到之后感觉到十分振奋。为什么呢?我们先来看一看PSS的大背景和大困惑吧。

- 尽管各种验证手段都推广出来,例如形式验证、逻辑仿真、emulation、虚拟建模和FPGA原型验证,这么多的平台却缺少三个缺席的粘合剂。它们分别是,跨平台的验证环境、跨平台的覆盖率合并手段和跨平台的激励形式。目前,跨平台的验证手段和覆盖率合并在各个EDA公司的推广下,已经有了可实现的手段。这两种粘合剂是由于多个验证形式的出现,而产生的用户需求,所以EDA公司可以在自身已有的工具套件下给出合理的解决方案。而这两种粘合剂还无法暂时统一化,这仍然受限于不同厂商的工具特性。

- 对于上面所述的第三个粘合剂,即跨平台的激励形式。它要解决的有两个层面,一个层面是在不同的验证平台中,完成跨平台的水平复用;另外一个层面,即是期望从模块一级到子系统一级再到芯片系统级的验证用例,可以得到垂直复用。

如果解决了第三个粘合剂,给水平复用和垂直复用带来更多的可能,我们不妨想象一下,在不久的将来,有没有一种可能是,平台软件、固件层和驱动层、硬件测试层都在使用同一套测试的描述语言,而基于同一种激励描述语言,这可以使得硬件测试层的用例为驱动层所复用,而平台软件层这一更高层的测试场景,也可以通过下移的方式,在硬件测试层通过emulation或者FPGA的方式来完成更早期的验证呢?如果第三个粘合剂,可以使得芯片设计的实现流程更早期地靠近软硬件协同开发,而不再只是简单地停留于理论层面。那么我们可以进一步地期待PSS标准在未来对验证技术在跨平台跨公司的统一化趋势。

实际上在早先年路桑就试用过Mentor Graphics的图形化验证工具Questa inFact,而目前对PSS标准作出同样突出贡献的Breker公司也凭借着Trek系列产品依靠图形化的验证方式和PSS的理念,可以自动产生UVM和C的用例(即凭借独一性的激励描述语言来进行具体测试语言C/UVM等的转化),来实现跨平台(simulator、emulator、FPGA和silicon)的水平复用和从IP级到芯片系统级的垂直复用。谈到这里,我们很难讲,EDA厂商们是不是“商量”好的,都在某一个趋势中希望开发出一款产品来抢占制高点,譬如Cadence家的Perspec System Verifier也有着相同的特性……

那么我们需要考虑EDA厂商们,为什么都会选择在相同的时间点布局相似特性的产品线呢?难道只是简单地为了“相腐相成”吗?可以说在PSS工作组2014年12月成立的时候,就注定了它的多小组多公司共同主导的特性,为的也是可以在所有小组和平台上实现测试场景的共享和重用。这里我们还需要记住一个人的名字,我想他作为该工作组的主席,在接下来的多年中对于验证和更高层面上的系统测试的贡献,会让我们肃然起敬,那就是Faris Khundakjie(Intel公司),他在最近过去的一年中也被Accellera授予了特别贡献奖。这位同事目前在Scalable Performance Development事业部,就任Server Tools and Methods部门的高级技术领导。

PSS工作组正是联合了多个IC业界公司和EDA厂商,才可以发起一个得到业界广泛期待的标准制定小组,而在过去的两年多的时间中,小组在标准草稿制定中也在充分吸取了各个成员的要求,目的在于给出可以跨平台和覆盖率地给出明确的限定、继承和复用的情形描述。所以,EDA厂商在目前SoC集成度日益提高,而原有仿真技术已经遇到显著瓶颈的时候,明显地开始联合业界IC公司内的验证专家,开始听取他们的意见,不但在现有工具的特性扩展上按照用户的意见做特性规划的制定,也在新标准新产品线的规划上面能够联合IC公司,共同制定标准(也可能从IC公司的原型工具中吸取“灵感”)。

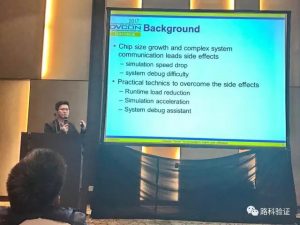

路桑有幸能够代表Intel Communication and Devices事业部,Baseband and SoC Development 西安研发中心来参加这一场盛会,并且作为simulation technology论文演讲环节的主讲嘉宾将英特尔西安SoC研发中心在最近几年中的验证效率提高实践分享给各个公司的技术专家。尽管全篇使用的英文演讲,路桑为可能表达的不清晰也担心过,然而在开篇的三分钟以后从听众的眼睛里就知道了一件重要的事情,那就是我分享的,正是他们需要的,他们在尽可能的捕捉我口中的每一个单词和屏幕上的每一幅幻灯片。而事实上,我就如何克服SoC仿真效率低下提出的三个有效方案:降低动态负载,仿真加速和系统调试自定义插件,得到了与会几乎所有人的兴趣。在接下来原本5分钟的提问环节中,问题如子弹般飞过来,而回答也另提问者们觉得值回了票价(路桑也是交了注册费不辞千里来的啊…)。即便如此,会后也有不少的朋友,对我们在仿真加速中提出的西安自主开发的虚拟处理器Wukong有着十足的兴趣。

大会在这一天的安排非常紧凑,不但在上午有各个公司给的最新工具和方法学的Tutorial培训环节,也有在下午的分为四个时下最热技术话题的论文演讲,同时还有可以碰撞出思想火花的Poster展示环节。本次大会提交入选的论文分别在技术演讲环节和poster海报展示环节中得到各自的机会去分享。路桑也饶有兴致地同poster场地的很多位论文作者们展开讨论,探寻他们的技术观点。路桑很负责任地说,poster环节的论文都有着非常不错的质量,其中有一些论文的核心观点很闪光。在技术论文演讲中,四个热点话题包含了UVM高级应用实践、GPU建模技术、低功耗验证和仿真技术。路桑所分享的论文《Best Practices over Enhancing SoC Verification Efficiency》就是仿真技术话题中的一篇。

在下午结束了技术论文演讲和poster展示之后,大会进入了晚宴环节。晚宴的keynote嘉宾邀请的是Synopsys公司的高级主管Fu Yong先生,他在晚会中分享的是近年来Synopsys在一轮轮的收购之后,在不断的吐纳完成新老血液的营养交换之后,给出的统一化的方案即:

- 最快的引擎:无论是最新的VCS2017.03还是Zebu-3 emulator(还有virtualizer、HAPS..),都将是各自领域的擎天柱

- VCS在simulation、emulation和prototyping环境之间的跨平台编译

- Verdi在从底层抽象级到高层抽象级的跨平台调试

- 鉴于统一编译和统一调试的优势带来的更高产出和性能的本地化集成

为什么要重点分享Synopsys接下来在验证领域的这一系统化的方案推广?Synopsys称之为verification continuum,重点不但在于“打包”贩卖,更在于他们是真心实意地通过系统化的解决方案来协调跨平台的问题,也就是路桑在之前谈到过的目前暂时由EDA厂商自定义解决的两种粘合剂,即跨平台的验证环境编译和调试问题,还有跨平台收集到的覆盖率合并问题。

无独有偶,在路桑过去的两个月同Synopsys和Cadence两家公司的技术研发部门主管的交流当中,发现了这前面两种粘合剂的惊人相似处。不妨看一看Cadence家关于跨平台收集覆盖率的合并问题提出的解决方案,即在不同的层次验证周期中,通过现有的工具JasperGold、Specman、Xcelium、Perspec和Palladium来收集来自于模块级、子系统及、芯片系统及和性能测试级的覆盖率,并且最终完成跨平台的覆盖率合并问题。

在Fu Yong先生的演讲中,也坦言他们对路桑在论文中谈到的一个SoC仿真优化方向感兴趣,即通过系统调试自定义工具来协助验证工程师们提高验证效率,并且拥有“上帝视角”,使得verifier们不再需要在芯片系统级测试中拘泥于具体的信号和总线协议,而是有条件关注于整个系统的寄存器状态、处理器的访问解读、NoC的实时性能捕捉…其实路桑还有很多干货和idea还没有抖出来,也许30分钟的技术演讲对于这么多的工程实践而言,有那么一些短吧…

对于路桑提到的这些系统调试的协助手段,为什么会得到厂商的关注呢?实际上厂商在之前的一次大客户走访中就尝鲜了路桑的这篇大会论文演讲,当时就对论文中的一些手段产生了浓厚的兴趣。在这里,路桑觉得,系统化的调试方式与Synposys在Verdi跨抽象级的调试设定策略上不谋而合。如果有更多的机会,也许将来路桑可以作为Verdi新特性的贡献者,将SoC系统调试上,关于功能(function)、效能(power)和性能(performance)在系统视角上提出更多的建议,可以将我们目前在自研发的系统调试工具的经验分享给Verdi,也从而让Intel在SoC系统级的调试经验造福和影响到更广的范围。

在稍后的颁奖环节中,经过了与会者每人手中的投票参与,路桑的技术演讲《Best Practices over Enhancing SoC Verification Efficiency》获得了最佳论文奖(Best Paper),而来自于Altran公司的Vinoth Kumar Subraman,他的论文《On the Fly Stimulus Generation for Coverage-Driven Functional Verification Based on Constraint Random》获得了最佳展示奖(Best Poster)。

得知得奖的那一刻,路桑和身边的朋友都非常激动,而路桑差一点就跳到主席台了……然而最终的合影里面,路桑还是以标志性的腼腆红获得了台下女粉丝的一致尖叫(信不信由你们)。如果让路桑分析这次得奖的原因,恐怕除了有1分的颜值加分,2分的英语口语不带陕西泡馍腔之外,还有7分的最佳实践分——要知道这7分可是真刀真枪真金白银的项目实践换来的。这分量不单单意味着上百人的验证团队在面对一个个新的验证瓶颈时给验证和策略组的吐槽和施压,也有着路桑和众多验证专家们优化升级现有验证方法和环境的日日夜夜,还离不开项目领导和验证掌门可以放手由我们去跳海遨游。路桑在论文中深深地感谢了领导(真心的亲),也感谢了参与到日常验证优化中的每一位工程师,正是Intel西安自由的合作氛围,使得我们有机会将好的idea,作为项目加速的助推器,给出十足的燃料,也正是有着一批批甘愿part time不计个人得失的工程师们,团结合作将好的idea能够落地。

也正如此,我们这一群“鸭”——可以春江水暖鸭先知,可以在EDA公司之前结合自身的需要,开发出丝毫不逊色的简单粗暴又好用的流程和工具,这也是我们论文中的观点可以引起IC工程师和EDA公司关注的原因。

同时,我们也要在这里感谢首届DVCon中国的组委,正是你们的辛劳和大力推广,使得躺在英特尔西安的“黑科技”能够从西北一路直飞保鲜空运到上海,同全国各地的验证工程师们一同分享这有趣有料有内涵的技术实践。我们也有理由相信,在不远的将来,英特尔西安会有更多的idea落地,在第一时间通过路科验证、DVCon和其它重要的行业会议展示给业内的验证工程师们。

最后,我要感谢演讲前的那两罐麒麟一番榨,是它的新鲜口感给了我更多的力量,让我可以讲到high!

如果想下载路桑的这一篇Best Paper,可以在订阅号中回复“dvcon2017”。

如果想知道关于DVCon上海更多的内容,可查看往期内容——

谢谢你对路科验证的关注,也欢迎你分享和转发真正的技术价值,你的支持是我们保持前行的动力。