题目:键入时纠正设计和验证编码错误

摘要:

很少有像大型复杂半导体器件的设计和验证那样令人畏惧的工程任务。一个设计师可能负责数百万个门,它将重用、适应和从头开始编码的逻辑。大多数大型设备都是SoC设计,在硬件和软件之间具有深层的嵌入式交互。验证工程师需要了解设计、嵌入式代码、测试台、底层生产软件,甚至可能是一些最终应用程序。

在这种复杂性背后,有一系列丰富的语言来捕获和验证SoC。最常用的是System Verilog,用于嵌入式软件和高级模型的硬件和测试平台以及C/C++。有许多库和其他构建块来帮助创建设计和验证环境,最显著的是通用验证方法(UVM)标准。然而,这些库本身非常复杂,有许多选项和变体,因此在编码和调试时很难牢记所有这些。

由于所有这些语言和库的复杂性,SoC团队可能希望在编写代码时获得某种帮助。常规的文本拼写和语法检查已经变得熟练,不仅能发现错误,而且还建议可能的修复方法。鉴于自然语言的定义要比计算机程序严格得多,所以对于SystemVerilog和其他设计和验证语言,期望类似或更好的自动化似乎完全合理。

IDE的价值

软件程序员熟悉集成开发环境(IDE)的概念,在IDE中他们可以编写和调试代码。近年来,获得一个IDE已经成为可能,该IDE支持甚至是最大和最复杂的SoC项目的全部硬件和软件创建、验证和调试。IDE可以使用所使用的语言和库在上下文中分析设计和验证代码。

IDE必须支持各种软件编程语言、建模语言、硬件描述语言(如Verilog和VHDL)、专用验证语言(如e)以及SystemVerilog的设计和验证功能。IDE可以:

- 对代码执行多种类型的检查

- 根据用户偏好突出显示和格式化代码

- 编译或解释代码以呈现完整的结构

- 连接到模拟器以调试失败的验证测试用例

- 提供直观的图形用户界面(GUI)

这组特性会对工程效率产生很大影响,将常见任务从几分钟或几小时减少到几秒钟。使用IDE可以使芯片计划缩短数周或数月,尤其是在大多数开发项目中,验证和调试消耗的资源最多。IDE的价值更大,它不仅可以检测代码中的错误并提供工程师键入的自动完成功能,还可以为解决代码错误和代码结构中的不一致之处提供建议。

IDE作为自动校正器

IDE可以建议修复程序并提供键入时自动校正的功能,这一点也就不足为奇了。除了编译器之外,IDE还有强大的分析引擎,可在幕后不断运行。每当工程师进行更改并更新完整设计和验证环境的内部数据库时,它都会重新读取源代码。该数据库必须支持SystemVerilog、Verilog、VHDL、E和C/C++中的输入,将所有设计和验证元素连接到一个结构中,并使跨越所有这些语言的分析得以实现。

利用这个数据库及其库和构建块的知识,IDE对设计人员和验证团队的意图有相当的洞察力。正如语法检查器使用其对自然语言约定的知识来建议更改一样,IDE利用其内部知识来提出更改,以解决它检测到的问题。当然,没有工具可以确切地知道工程师的意图,因此在对代码进行任何更改之前,必须接受建议。

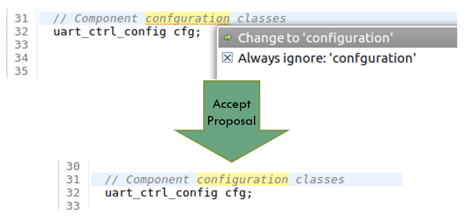

如图1所示,IDE的建议以熟悉的拼写检查开始,包括接受或忽略任何建议的修复的选项。如果接受,将自动对代码进行更改。建议的拼写更改仅针对注释和文本字符串提供,因为不同的语法规则适用于其余代码。第一个屏幕截图和后面的其他截图显示了来自AMIQ EDA的设计和验证工具(DVT)Eclipse IDE的示例。

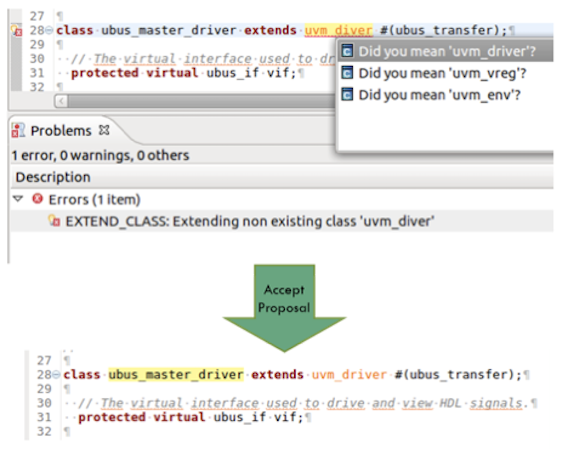

检测到的问题和建议的解决方案的范围远远超出文字处理工具提供的简单拼写检查。因为IDE编译了完整的设计和验证环境,所以它具有完整的代码范围,并且可以识别出大量的不一致性。例如,IDE可以检测标识符中的印刷错误。在图2中,用户输入了对UVM组件的错误引用,IDE建议了一些可能符合用户意图的实际名称。建议列表中的第一个条目已被接受,然后在代码中自动更新引用。

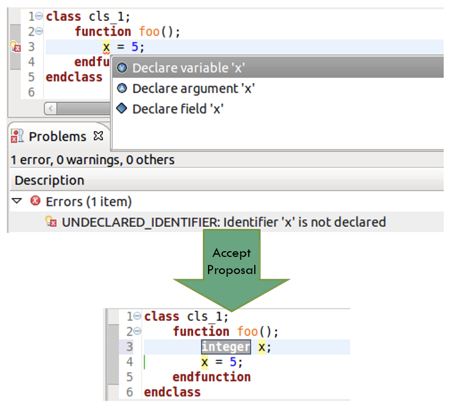

如果用户键入了对尚未声明的变量的引用,IDE不仅会检测到这一点,而且会提出修复方法。如图3所示,如果建议被接受,那么声明将自动插入到代码的适当位置。

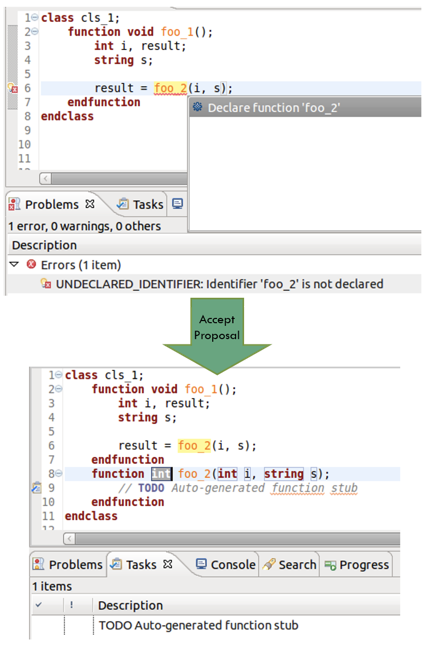

在另一个键入时自动更正的示例中,图4显示了一个类定义,其中用户调用了一个尚未声明的方法。IDE建议添加一个实现,但是由于它无法知道函数应该做什么,它只在代码中插入一个存根。存根包含一个特殊的“TODO”编译指示来提醒工程师完成实现,并将此完成作为一个条目添加到项目任务列表中。

虽然图4中没有显示,但IDE也可以用类似的方式检测丢失的外部任务或函数实现,并在类范围之外插入存根。

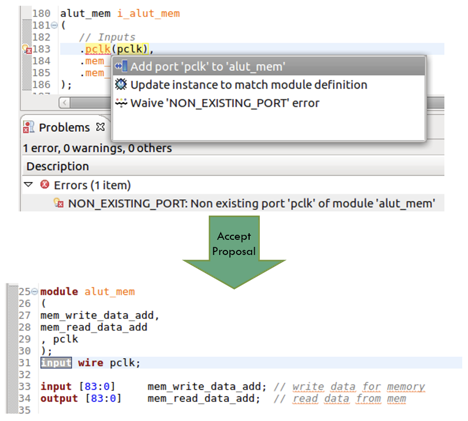

有时被引用的模块存在,但没有特定端口。图5显示了一个实例化已定义模块的示例,尽管实例中的端口之一不在定义中。IDE提供了以下选项:放弃错误、自动更新实例以删除有问题的端口并与定义匹配,或自动更新定义以添加缺少的端口。“添加”选项是屏幕截图中选择的选项。

IDE还可以检测丢失的模块参数并将它们添加到定义中。这些类型的省略在编码的早期阶段经常发生,因为模块和类正在被定义和使用,可能是由不同的工程师执行的。IDE的检查和建议在项目后期更具价值。当定义或实例化被单方面更新时,将发生编译错误。工程师们省去了整理这一问题的麻烦;IDE一输入就会检测到不一致,并提出可能的解决方案。

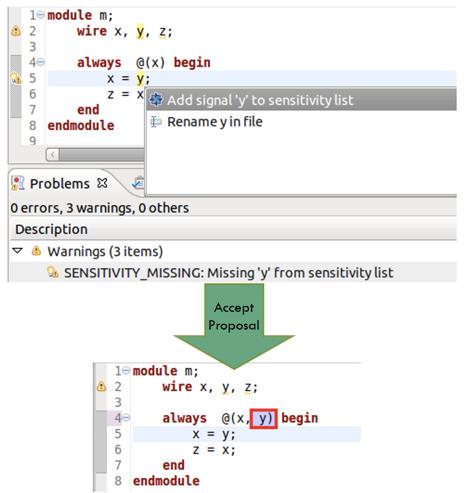

在编写SystemVerilog(或Verilog)时,有一种特别隐蔽的省略形式:在敏感度列表中缺少一项。只有当列表中至少有一个项更改了其值时,才会评估此类列表中的代码。这是有风险的,因为忽略信号可能会导致在合成过程中插入锁存器,这通常是不可取的。图6显示了一个示例,其中只列出了一个变量(’x’),尽管敏感度列表所涵盖的代码中也使用了变量’y’。

在这种情况下,如果“y”的值要更改而“x”没有更改,则两个更新将丢失,“x”和“z”将保留其旧值。这种编码错误在模拟中很难触发和调试,需要大量的回溯来找到错误数据的来源。IDE提供了一个更有效的解决方案,通过查找和报告缺失的变量,并建议将其添加到敏感度列表中。在图6中,建议已被接受,并且“y”已自动添加到列表中。

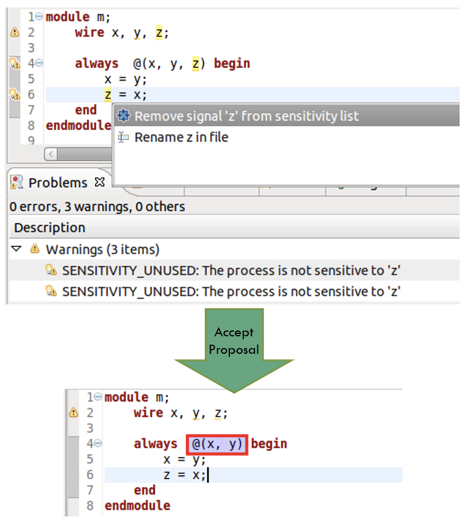

就像模块定义和实例化一样,敏感度列表和其中的代码在进行单方面更改时可能会变得不一致。有时工程师可能会删除一个变量,但忘记从列表中删除它。这不会导致任何功能错误,但代码看起来很混乱,并且由于不必要的评估,模拟可能会降低效率。如图7所示,IDE还检测敏感度列表中的伪变量,并建议自动删除它们。

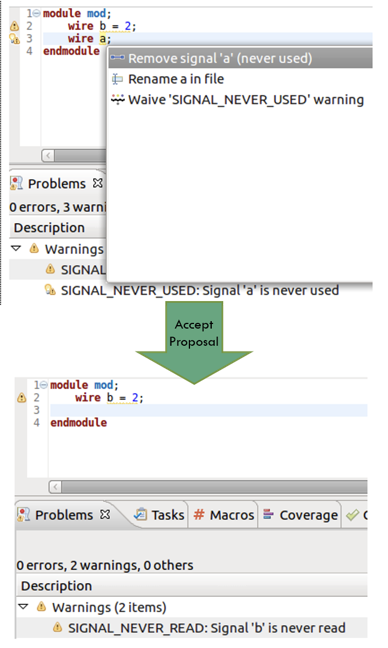

在相关的方面,IDE可以检测和报告已声明但从未在代码中实际使用的信号。图8显示了一个这样的信号;IDE提供了放弃警告、删除信号或重命名信号的选择。这里,选择了“remove”选项,因此信号声明被自动删除。图中还显示了IDE的另一项有用检查:检测信号何时被分配了一个值,但该值从未使用。这可能是一个错误,或者只是编码仍在进行中的结果。

结论

芯片设计和验证是一项庞大的任务。大量带有许多相似的标识符的代码使它变得复杂。印刷错误、缺少声明和不一致的引用会导致验证失败,并可能导致数小时的繁琐调试。IDE的“键入时自动校正”功能不仅可以发现问题,还可以提出解决方案和自动更新,从而使这项任务变得更加容易。由此产生的效率和项目时间的减少使得使用复杂的IDE成为一个明确的需求。

进一步阅读

本文是系列文章中的第三篇(https://www.techdesignforums.com/practice/technique/correct-design-and-verification-coding-errors-as-you-type/);

单击此处查看第一部分(https://www.techdesignforums.com/practice/technique/why-hyperlinks-are-essential-for-hdl-debugging/),

单击此处(https://www.techdesignforums.com/practice/technique/auto-complete-ide/)查看第二部分。

单击此处(https://dvteclipse.com/products/dvt-eclipse-ide)了解有关hdl上下文中的超链接和eclipseide工具的更多信息。

原文链接:

DVT工具对于学习SV/UVM和验证环境开发具有很大的帮助,现已是V2Pro课程的一部分。扫描下方二维码可直达课程页面,马上试听。

扫描上图二维码可直达课程页面,马上试听

往期精彩:

理解UVM-1.2到IEEE1800.2的变化,掌握这3点就够