设计和验证一个大型、复杂的半导体器件都是与编码有关。设计意味着绘制大量的原理图,并使用手工指定的输入值实时进行验证,输出结果以波形形式观察的日子已经一去不复返了。当然,可能仍然有一个或两个模拟功能的示意图,并且波形在调试中仍然扮演着重要的角色。但是硬件设计、片上系统(SoC)中的嵌入式软件以及大部分验证测试平台都是编码的。

一个典型的设计和验证环境使用丰富的语言组合,包括SystemVerilog、Verilog、VHDL、E和C/C++,将所有的设计和验证元素互连在一起。除了代码的功能正确性之外,还有许多属性决定了逻辑综合、编译器和其他工具对代码的处理能力,以及工程师对其进行支持、调试和改进代码的容易程度。即使是一致对齐和缩进这样的简单属性也可以使代码更易于理解和维护,特别是当新工程师遇到它时。

为了让工程师和工具更好地使用代码,改进代码的过程通常被称为“重构”。这个过程不是为了发现或修复代码中的错误,而是为了提高代码的可理解性和可支持性。在实践中,重构可以很好地揭示隐藏在“混乱”中的错误,并在更好的代码中通过检查变得可见。尽管传统的重构主要是手工完成的,但是设计和验证代码的许多重构步骤现在可以在交互式环境中自动执行。

用IDE重构

集成开发环境(integrateddevelopmentenvironment,IDE)最初是为软件开发而开发的,是一种帮助程序员以交互方式开发、测试和调试代码的工具。IDEs的范围已经扩展到支持硬件设计师和软件工程师创建设计和验证测试台的过程。IDE可以支持各种软件编程语言、建模语言、硬件描述语言(如Verilog和VHDL)、专用验证语言(如e)以及SystemVerilog的设计和验证功能。IDE可以:

- 对代码执行多种类型的检查;

- 根据用户偏好突出显示和格式化代码;

- 编写代码,给出完整的设计和测试平台结构;

- 连接到模拟器以调试失败的验证测试用例;

- 以及为代码开发提供直观的图形用户界面(GUI)。

在GUI背后有很多智能在起作用。IDE实际上会编译源代码并构建设计和验证环境的内部数据库。这允许使用所使用的语言和库(如通用验证方法(UVM))的知识在上下文中分析设计和验证代码。这个数据库和提取的知识使代码能够自动更改和改进,所有这些都可以在使用IDE的工程师的轻松控制下进行。

自动重构的示例

使代码看起来“漂亮”也许是IDE能够执行的最明显的改进。如前所述,即使是非常简单的格式更改也会使代码更易于理解、验证和修改。尽管重新格式化不总是被认为是重构的一种形式,但其是合格的,因为它可以在不更改功能的情况下改进代码。一些基本的重构操作包括:

- 根据范围自动缩进代码;

- 从行尾修剪空白;

- 将空白压缩为单个字符(当它不影响缩进时);

- 在用户指定的空格中混合多个制表符和空格;

- 在指定的标记之前或之后添加空格;

- 包装线过长;

- 以及换行多行注释以适应行宽度。

虽然这些更改听起来微不足道,但IDE的自动化可以为工程师节省许多时间,使他们在手动编辑上花费大量时间,以符合公司的编码准则。对语言语法和语义的深入了解使IDE能够进行更复杂的代码操作,包括:

- 如果语句可选,则插入“begin”–“end”块;

- 在新行上放置“if”和“else”结构;

- 将模块端口和参数、函数和任务参数以及类参数每行一个或多个放在一行上;

- 缩进单行和/或多行注释;

- 以及缩进指定语言结构。

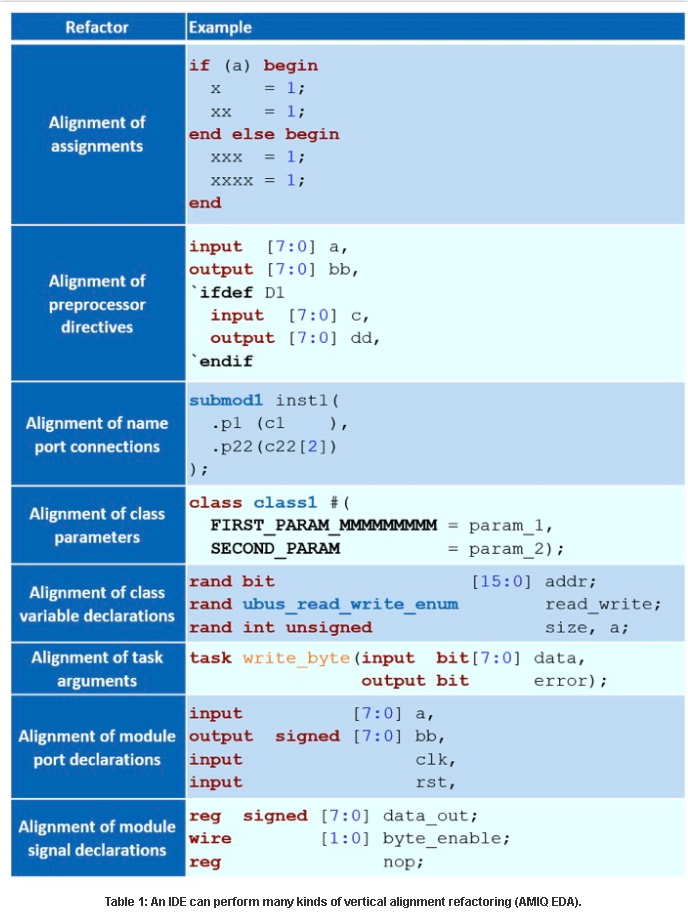

所有这些重构步骤以及本文中讨论的其他步骤都是自动化的,但完全由用户控制。有些公司可能允许个别工程师选择自己的格式首选项;有些公司可能需要使用公司范围内的配置文件,以便所有代码看起来一致。构件的垂直对齐是工程师通常有强烈偏好的另一个领域。表1显示了几种自动化的对齐方式,它们使设计和验证代码更易于理解和维护。所有这些都可以由IDE执行。

尽管本文中提供的示例集中在SystemVerilog代码上,但是重构的原则同样适用于所有的设计和验证语言。

在这种最简单的重构形式中,代码既不在语法上也不在语义上发生变化。然而,有些重构操作在语法上改变了代码而不改变其黑盒功能。任何设计或验证工具的SystemVerilog前端都应该从重构前后的代码中构建完全相同的内部模型。SystemVerilog是一种非常复杂的语言,有1300多页的参考手册。有许多方法可以指定等效功能。灵活性有时会滋生复杂性。其中一些方法比其他方法更紧凑、可读和可维护。此外,由于不同的项目团队可能有不同的编码风格和规则,重构的能力对遵循编码准则有很大帮助。

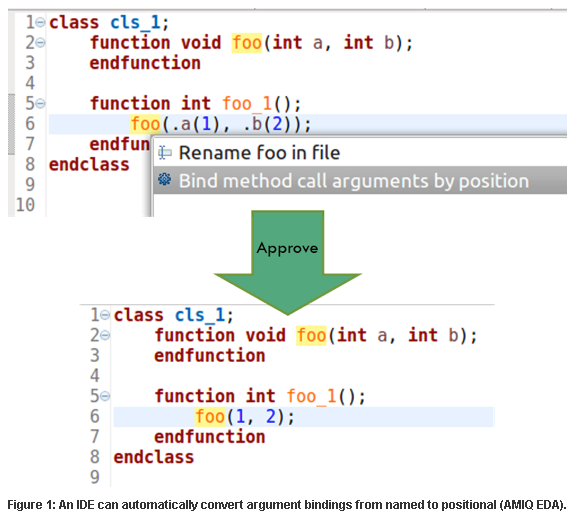

SystemVerilog的一个有用但有时令人困惑的灵活性特性是,模块实例端口连接和函数调用参数可以通过位置或名称指定。位置语法具有简洁的优点,但是代码可能很难读取,特别是当包含许多相同类型的参数或端口时。命名语法提高了可读性,并且对参数或端口顺序不敏感。图1显示了IDE自动将命名参数绑定转换为位置参数绑定的示例。这个屏幕截图和下面示例中出现的其他截图来自AMIQ EDA的设计和验证工具(DVT)Eclipse IDE。

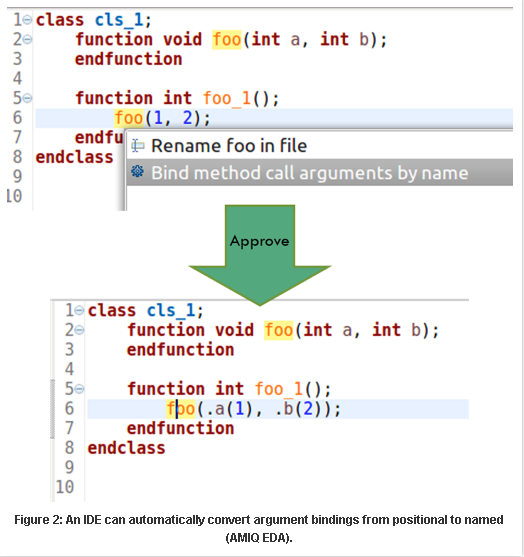

当进行代码清理或重用遵循不同编码规则的以前项目中的代码时,能够从一种形式的参数绑定切换到另一种形式,这是非常有用的。图2显示了IDE自动将位置参数绑定转换为命名参数绑定的示例。此功能还可以用于统一编码样式,或者可以临时用于检查函数调用或实例化是否正确。

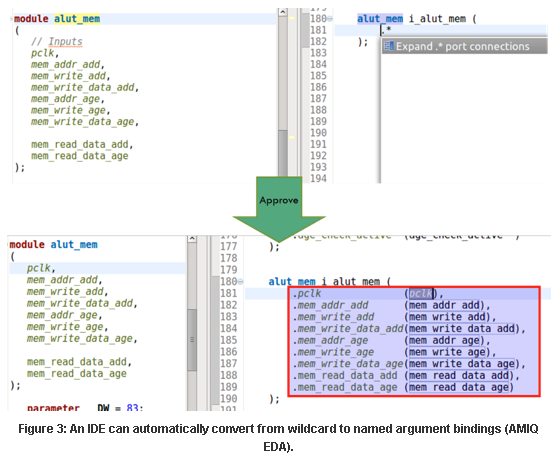

SystemVerilog还支持“.*”通配符运算符,这表示所有端口都隐式连接到实例化范围内现有的同名信号。如果可能,这是一个非常紧凑的表单,但有时用户可能希望将通配符扩展为完整的端口列表。图3显示了执行此重构的IDE。

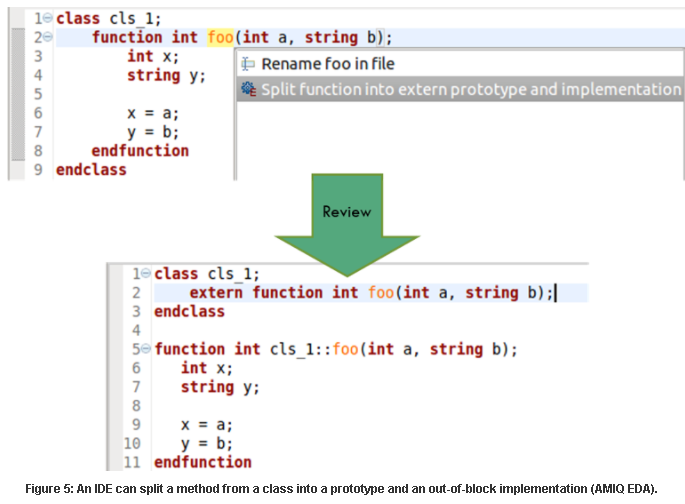

SystemVerilog为灵活性提供了许多其他选项。例如,类方法可以在类本身中实现,也可以只是使用块外实现的原型。IDE可以自动重新组织代码以在这两个选项之间切换。图4显示了一个折叠到该类中的外部方法实现,而图5显示了一个拆分为外部的内部实现。

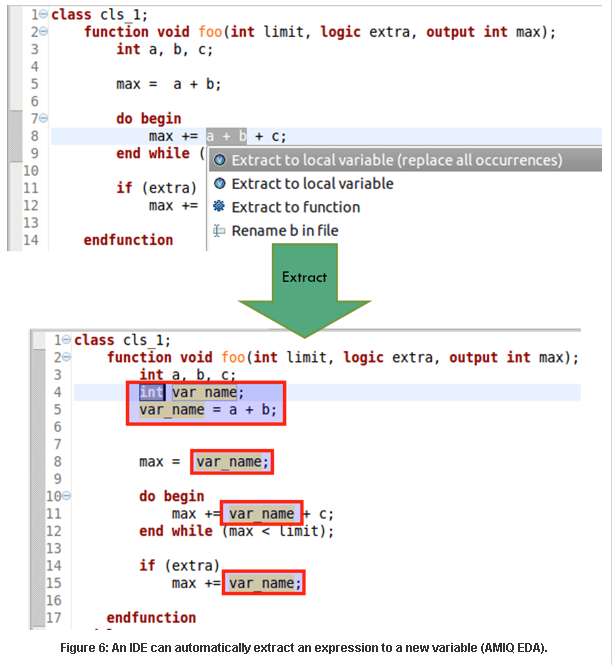

另一种导致代码更紧凑、更可读的重构方法是用局部变量替换重复表达式。图6显示了使用IDE进行此类更改的示例。表达式“a+b”在同一个函数中出现多次,因此用户指定创建一个新变量来替换此表达式,然后根据需要命名该变量。

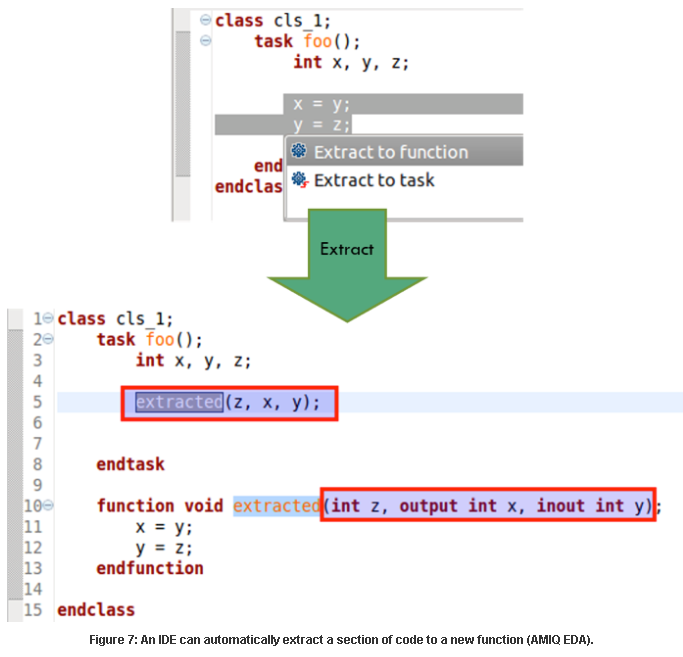

类似地,用户可能有一个代码块需要重复,因此将其转换为新的函数或任务将创建更紧凑的代码。有了一个精心挑选的名字,代码也会更容易理解。图7显示了IDE从用户指定的代码部分创建函数。用户还可以选择新函数的名称。

一旦创建了新函数,就可以在以后的编码中使用它,只要它有意义。工程师并不总是用定义明确的库来启动项目。他们可能会在编写代码时发现重用机会,并且动态重构和创建新的可重用任务和函数的能力非常有价值。

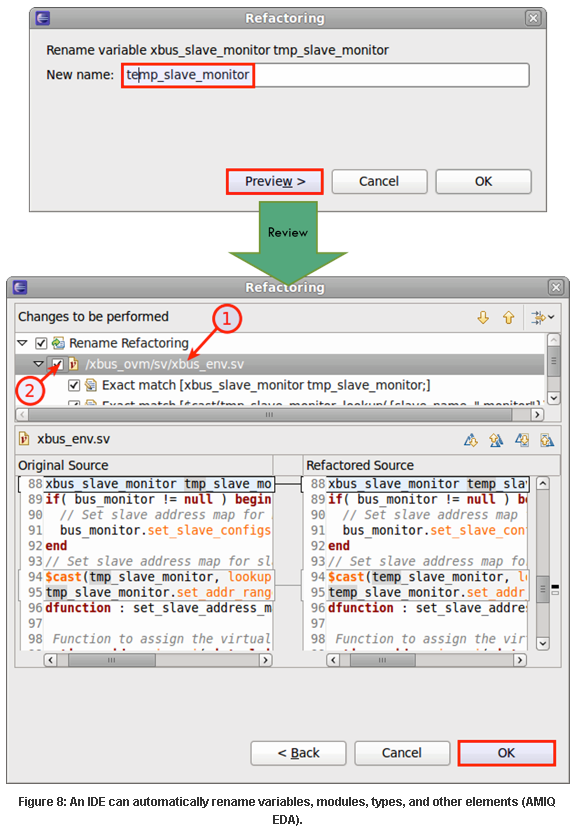

重命名代码中的元素是最流行的重构操作之一。当使用纯文本编辑器编写代码时,这个看似简单的任务很难执行。例如,更改类型的名称可能涉及到对许多文件的编辑,而文本编辑器搜索可能需要繁琐的验证,因为其他元素具有相似或相同的名称。图8显示了这个过程如何在IDE中更好地工作。用户选择要更改的元素(在本例中为变量)并键入新名称。IDE显示所有将受名称更改影响的文件,用户可以预览每个文件中建议的更改。批准后,所有相关文件将自动修改,IDE的内部数据库也将更新。IDE允许用户轻松地重命名多种元素,包括模块端口、类、函数、宏、变量和参数。

结论

SystemVerilog的复杂性以及设计和验证代码的不同规则意味着不同的团队在他们的开发过程中可能会采取不同的方法。IDE的自动重构提供了一种有效的方法,可以将所有代码转换为遵循一组通用规则的通用格式。它还通过消除冗余来生成更紧凑的代码,从而使代码更具可读性和可维护性。这既节省了时间又节省了资源,这也是IDE成为设计和验证项目必备的原因之一。

延伸阅读

本文是系列文章中的第四篇;单击此处查看第一部分,单击此处查看第二部分,单击此处查看第三部分。单击此处和此处了解有关使用hdl和Eclipse IDE工具重构的更多信息。

原文链接:https://www.techdesignforums.com/practice/technique/refactoring-design-verification-code/

DVT工具对于学习SV/UVM和验证环境开发具有很大的帮助,现已是V2Pro课程的一部分。扫描下方二维码可直达课程页面,马上试听。

扫描上图二维码可直达课程页面,马上试听

往期精彩:

路科发布| 稳中带涨!25w成芯片校招薪资平均底!2020应届秋招数据全面分析!

理解UVM-1.2到IEEE1800.2的变化,掌握这3点就够