路科验证官网首页:路科验证 – 专注于数字芯片验证的系统思想和前沿工程领域

EETOP路科首页: EETOP – 路科验证 – IC验证培训

CSDN路科首页:CSDN – 路科验证 – IC验证培训

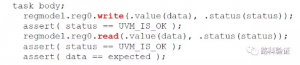

不少路粉对寄存器模型的使用可能还停留在这个阶段:

也就是说,通过寄存器句柄,配合读写指令,即可完成一次总线上的访问。

当然,你也可以通过指定BACKDOOR,来做后门访问。这两种方式在红宝书中,我们都已经详细介绍过了。今天路桑再来介绍一点儿不一样的,针对一些特殊的寄存器,有的时候这个寄存器可能是未映射的、非线性连续的,又或者需要通过BURST模式才能访问,总之无法通过一次SINGLE总线数据传输完成读写,这个时候,我们就可以考虑采用自定义的前门序列来实现了。

所以,今天路桑带来了一篇DVCon 2017的论文,Doing Funny Stuff with the UVM Register Layer: Experiences Using Front Door Sequences, Predictors, and Callbacks,来自于Dolous的John Aynsley,来深入谈一谈如何使用自定义的register sequence,来完成前门以及后门访问。

自定义前门访问序列

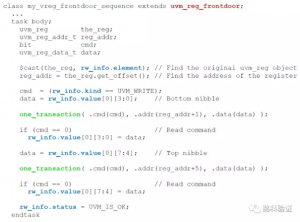

从这张图上可以看到,原有的前门访问是通过将寄存器级别的操作类型经过adapter转换为了总线级别的transanction,或者利用其反向路径完成转换,作为响应数据交回给寄存器模型一侧。当我们无法通过在adapter中使用bus transaction,而是需要通过多次bus transaction的组合来完成一次复杂的寄存器访问时,我们就可以使用用户自定义的寄存器前门序列,下面给出一段代码。

其中,rw_info是uvm_reg_item类型,是uvm_reg_frontdoor的成员变量,该对象包含着用来读写的目标uvm_reg的信息,譬如rw_info.kind为读写类型,rw_info.value表示读写数据,rw_info.status表示访问状态。在下面这个例子中,即是通过寄存器模型中的一个“虚拟寄存器”,其内容非连续分布在DUT中。因此,对于该寄存器的一次读写操作,实际上需要转换为两次读或者写操作,才可以通过两次访问非连续的地址,对其中片段数据完成操作才最终实现了该“虚拟寄存器”的读写操作。

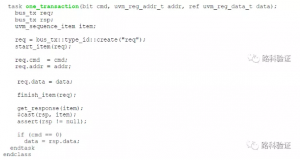

其中task one_transaction的定义很直观:

因此,在顶层env中在对寄存器模型完成了build以后,我们还可以创建my_vreg_frontdoor_sequence,并且通过指定regmodel.bus.reg0.set_frontdoor(frontdoor)来指定在访问该sequence时,需采取专用的frontdoor sequence完成寄存器访问。

这种用户自定义的前门访问方式,作为传统的register model + adapter + bus sequencer方式的补充,使得面对更为复杂的寄存器访问时,我们依然可以灵活应对。

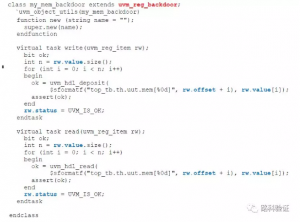

自定义后门访问序列

对于常用的后门访问,套路也已经为路粉们熟知了吧(不懂就去看红宝书喽),不过资深一点的verifier都知道,这种方法也主要是应对访问寄存器的,因为寄存器往往由reg类型(Verilog)来实现,容易做到HDL路径的映射。然而对于存储可不太一样,这是由于我们无法针对存储中的每一个地址都做到映射(会累死的吧)。不过考虑到大部分的存储模型都是一些reg数组,我们只需要做一些从访问地址到DUT存储模型数组索引的映射,再配合自定义后门访问序列就可以解决这个头疼的问题。

从下面的代码可以看到,通过自定义后门访问序列,结合UVM DPI函数uvm_hdl_deposit/uvm_hdl_read,实现了内存模型的批量读写(for loop提供)。

除了上面路桑谈到的这两个与大家接下来可能相关的寄存器模型使用方法以外,该论文还有一些其它的有趣应用,例如uvm_reg_callback用来对一些特殊的寄存器访问做读写前后的处理。如果这篇论文正说中了你现在面临的问题,你可以到资源页中去下载,链接如下: